## **O-RAN WG7**

## Hardware Reference Design Specification for Indoor Picocell (FR1) with Split Architecture Option 8

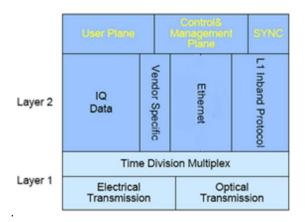

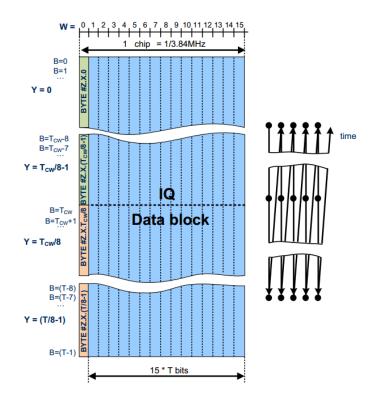

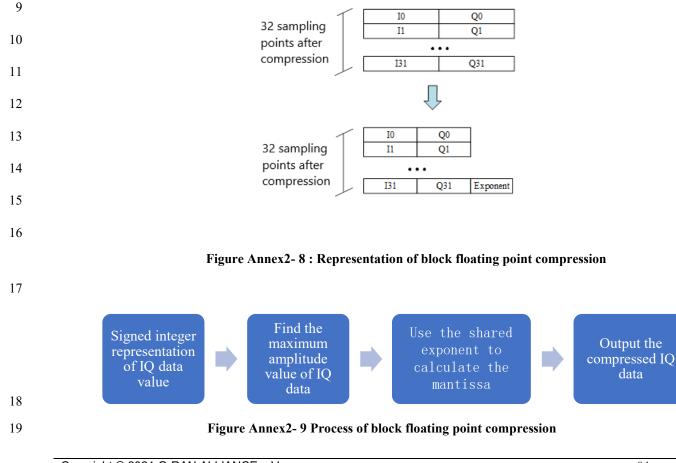

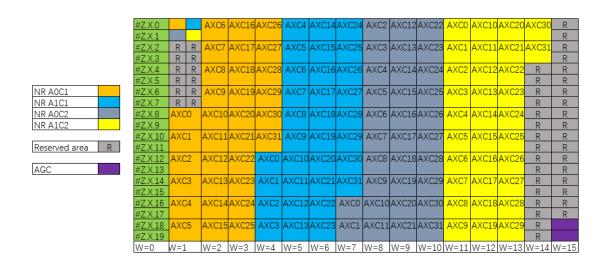

### This is a re-published version of the attached final specification.

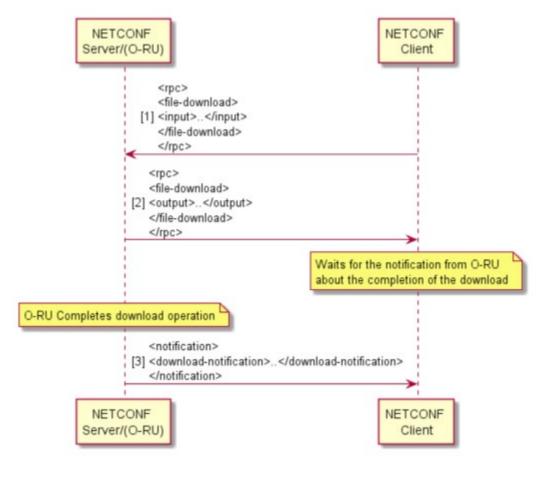

For this re-published version, the prior versions of the IPR Policy will apply, except that the previous requirement for Adopters (as defined in the earlier IPR Policy) to agree to an O-RAN Adopter License Agreement to access and use Final Specifications shall no longer apply or be required for these Final Specifications after 1st July 2022.

The copying or incorporation into any other work of part or all of the material available in this specification in any form without the prior written permission of O-RAN ALLIANCE e.V. is prohibited, save that you may print or download extracts of the material on this site for your personal use, or copy the material on this site for the purpose of sending to individual third parties for their information provided that you acknowledge O-RAN ALLIANCE as the source of the material and that you inform the third party that these conditions apply to them and that they must comply with them.

ORAN.WG7.IPC-HRD-Opt8.0-v03.00 Technical Specification

## **O-RAN WG7**

## Hardware Reference Design Specification for Indoor Picocell (FR1) with Split Architecture Option 8

Copyright © 2021 by O-RAN ALLIANCE e.V.

By using, accessing or downloading any part of this O-RAN specification document, including by copying, saving, distributing, displaying or preparing derivatives of, you agree to be and are bound to the terms of the O-RAN Adopter License Agreement contained in the Annex ZZZ of this specification. All other rights reserved.

O-RAN ALLIANCE e.V. Buschkauler Weg 27, 53347 Alfter, Germany Register of Associations, Bonn VR 11238 VAT ID DE321720189

## 1 Revision History

| Date       | Revision | Author | Description             |

|------------|----------|--------|-------------------------|

| 07/12/2021 | v03.00   | WG7    | Final Published Version |

2

<sup>© 2021</sup> O-RAN Alliance All Rights Reserved

## 1 Contents

| 2  | Revision  | History                                               | .2  |

|----|-----------|-------------------------------------------------------|-----|

| 3  | Chapter 1 | Introductory Material                                 | .8  |

| 4  | 1.1       | Scope                                                 | . 8 |

| 5  | 1.2       | References                                            | . 8 |

| 6  | 1.3       | Definitions and Abbreviations                         | . 9 |

| 7  | 1.3.1     | Definitions                                           | . 9 |

| 8  | 1.3.2     | Abbreviations                                         | . 9 |

| 9  | Chapter 2 | Hardware Reference Design 1                           | 13  |

| 10 | 2.1       | O-CU Hardware Reference Design                        | 13  |

| 11 | 2.2       | O-DU <sub>8</sub> Hardware Reference Design           | 13  |

| 12 | 2.2.1     | O-DU <sub>8</sub> High-Level Functional Block Diagram | 13  |

| 13 | 2.2.2     | O-DU <sub>8</sub> Hardware Design Description         | 14  |

| 14 | 2.2.3     | O-DU <sub>8</sub> Hardware Components                 | 15  |

| 15 | 2.2.3.1   | Digital Processing Unit                               | 15  |

| 16 | 2.2.3.2   | Hardware Accelerator                                  | 16  |

| 17 | 2.2.3.2.1 | Accelerator Design Solution 1                         | 16  |

| 18 | 2.2.3.2.2 | Accelerator Design Solution 2                         | 20  |

| 19 | 2.2.3.2.3 | Accelerator Design Solution 3                         | 23  |

| 20 | 2.2.3.2.4 | Accelerator Design Solution 4                         | 26  |

| 21 | 2.2.3.3   | Baseboard Management Controller                       | 27  |

| 22 | 2.2.4     | Synchronization and Timing                            | 27  |

| 23 | 2.2.4.1   | Synchronization and Timing Design 1                   | 27  |

| 24 | 2.2.4.2   | Synchronization and Timing Design 2                   | 28  |

| 25 | 2.2.5     | External Interface Ports                              | 29  |

| 26 | 2.2.6     | O-DU <sub>8</sub> Firmware                            | 30  |

|    |           |                                                       |     |

#### ORAN.WG7.IPC-HRD-Opt8.0-v03.00

| 1  | 2.2.7     | Mechanical                                             | 51  |

|----|-----------|--------------------------------------------------------|-----|

| 2  | 2.2.8     | Power Unit                                             | 32  |

| 3  | 2.2.9     | Thermal                                                | \$4 |

| 4  | 2.2.10    | Environmental and Regulations                          | \$4 |

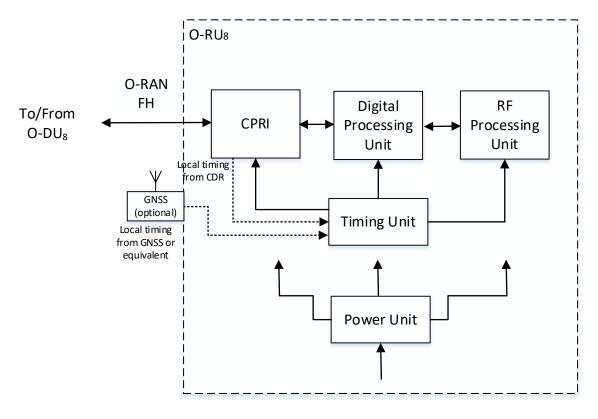

| 5  | 2.3       | O-RU <sub>8</sub> Hardware Reference Design            | \$5 |

| 6  | 2.3.1     | O-RU <sub>8</sub> High-Level Functional Block Diagram  | \$5 |

| 7  | 2.3.2     | O-RU <sub>8</sub> Hardware Components                  | \$5 |

| 8  | 2.3.2.1   | Digital Processing Unit                                | 57  |

| 9  | 2.3.2.2   | RF Processing Unit                                     | 0   |

| 10 | 2.3.2.2.1 | Transceiver Reference Design 4                         | 10  |

| 11 | 2.3.2.2.2 | Power Amplifier (PA) Reference Design 4                | 6   |

| 12 | 2.3.2.2.3 | Low Noise Amplifier (LNA) Reference Design4            | 8   |

| 13 | 2.3.2.2.4 | RF Switch Reference Design                             | ;0  |

| 14 | 2.3.2.2.5 | Antenna Reference Design5                              | ;3  |

| 15 | 2.3.3     | Synchronization and Timing5                            | ;3  |

| 16 | 2.3.4     | External Interface Ports5                              | ;8  |

| 17 | 2.3.5     | Mechanical                                             | ;9  |

| 18 | 2.3.6     | Power Unit                                             | 50  |

| 19 | 2.3.7     | Thermal $\epsilon$                                     | 51  |

| 20 | 2.3.7.1   | Environmental and Regulations                          | 51  |

| 21 | 2.4       | FHGW <sub>8</sub> Hardware Reference Design            | 52  |

| 22 | 2.5       | FHGW <sub>8</sub> High-Level Functional Block Diagram6 | 52  |

| 23 | 2.6       | FHGW <sub>8</sub> Hardware Components6                 | 53  |

| 24 | 2.6.1     | Digital Processing Unit                                | 53  |

| 25 | 2.6.2     | Synchronization and Timing                             | 55  |

| 26 | 2.6.3     | External Interface Ports6                              | 66  |

| 27 | 2.6.4     | Mechanical                                             | 58  |

|    |           |                                                        |     |

| 1  | 2.6.5         | Power                                                  |                           |

|----|---------------|--------------------------------------------------------|---------------------------|

| 2  | 2.6.6         | Thermal                                                |                           |

| 3  | 2.6.7         | Environmental and Regulations                          |                           |

| 4  | Annex 1       | Parts Reference List                                   | 70                        |

| 5  | Annex 2       | CPRI specification reference designErro                | or! Bookmark not defined. |

| 6  | Annex 3       | Option 8 CPRI spec reference design – Management plane |                           |

| 7  | Annex ZZZ     | Z O-RAN Adopter License Agreement                      | 179                       |

| 8  | Section 1: D  | DEFINITIONS                                            |                           |

| 9  | Section 2: C  | OPYRIGHT LICENSE                                       |                           |

| 10 | Section 3: F  | RAND LICENSE                                           |                           |

| 11 | Section 4: T  | ERM AND TERMINATION                                    |                           |

| 12 | Section 5: C  | ONFIDENTIALITY                                         |                           |

| 13 | Section 6: If | NDEMNIFICATION                                         |                           |

| 14 | Section 7: L  | IMITATIONS ON LIABILITY; NO WARRANTY                   |                           |

| 15 | Section 8: A  | SSIGNMENT                                              |                           |

| 16 | Section 9: T  | HIRD-PARTY BENEFICIARY RIGHTS                          |                           |

| 17 | Section 10:   | BINDING ON AFFILIATES                                  |                           |

| 18 | Section 11:   | GENERAL                                                |                           |

## 20 Tables

| 21 | Table 2-1: The Processor Feature List          | .15 |

|----|------------------------------------------------|-----|

| 22 | Table 2-2: The Memory Channel Feature List     | .15 |

| 23 | Table 2-3: Accelerator Hardware Component List | .17 |

| 24 | Table 2-4: Accelerator Hardware Feature List   | .23 |

| 25 | Table 2-5: Accelerator Firmware Feature List   | .24 |

| 26 | Table 2-6: Accelerator Hardware Feature List   | .26 |

| 27 | Table 2-7: Accelerator Firmware Feature List   | .26 |

| 28 | Table 2-8: External Port List                  | .29 |

| 29 | Table 2-9: Power supply unit feature list      | .34 |

| 1  | Table 2-10: Environmental Features                                     | 34 |

|----|------------------------------------------------------------------------|----|

| 2  | Table 2-11: Resource requirement for 2T2R O-RU8                        |    |

| 3  | Table 2-12: Resource requirement for 4T4R O-RU <sub>8</sub>            |    |

| 4  | Table 2-13: Interface requirements of the Transceiver                  | 40 |

| 5  | Table 2-14: Payload with DPD in Digital Device (GBPS Rx/Tx)            | 41 |

| 6  | Table 2-15: Payload with DPD in Transceiver (GBPS Rx/Tx)               | 41 |

| 7  | Table 2-16: RF specifications in Transceiver                           | 42 |

| 8  | Table 2-17: PA Requirements                                            | 46 |

| 9  | Table 2-18: Interface requirements of the transmit PA                  | 47 |

| 10 | Table 2-19: One stage LNA Requirements                                 | 48 |

| 11 | Table 2-20: Two stage LNA Requirements                                 |    |

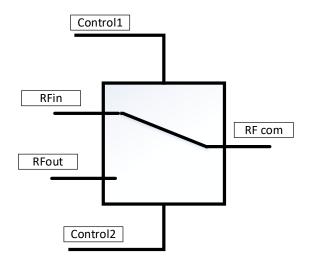

| 12 | Table 2-21: Interface requirements of the RF switch                    |    |

| 13 | Table 2-22: RF Switch Requirements                                     | 51 |

| 14 | Table 2-23: Antenna Requirements                                       | 53 |

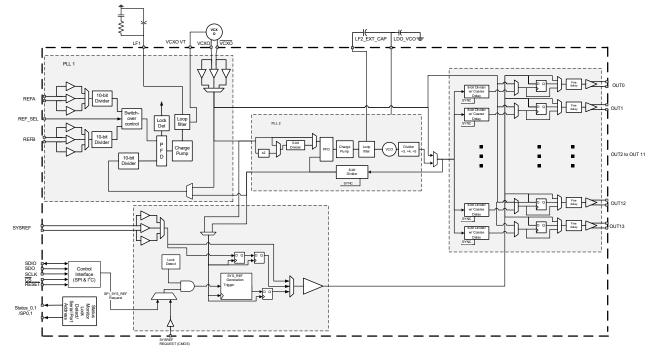

| 15 | Table 2-24: Interface requirements of the clocking                     | 55 |

| 16 | Table 2-25: Clocking RF requirements                                   | 55 |

| 17 | Table 2-26: External Port List                                         |    |

| 18 | Table 2-27: Power unit requirement for 2T2R and 4T4R O-RU <sub>8</sub> | 60 |

| 19 | Table 2-28: Power unit function                                        | 60 |

| 20 | Table 2-29: Environmental Features.                                    | 61 |

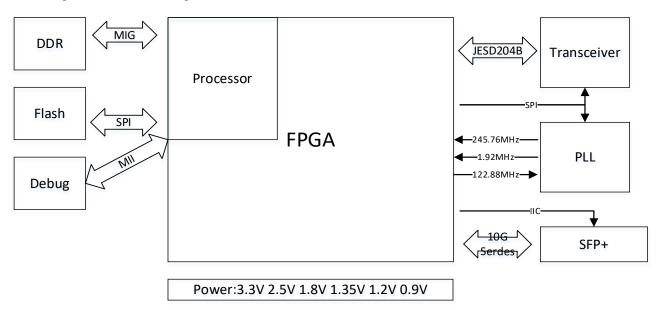

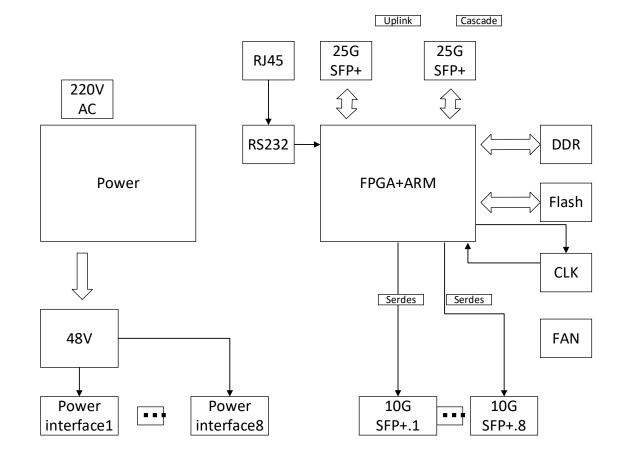

| 21 | Table 2-30: Interface requirements of the FPGA                         | 63 |

| 22 | Table 2-31: FPGA Resource usage for FHGW <sub>8</sub>                  | 64 |

| 23 | Table 2-32: Requirements of the PLL device                             | 65 |

| 24 | Table 2-33: External Port List                                         | 66 |

| 25 | Table 2-34: Requirements of the power unit                             | 68 |

## **Figures**

26

| 28 | Figure 2-1: O-DU <sub>8</sub> Functional Block Diagram                              | 14 |

|----|-------------------------------------------------------------------------------------|----|

| 29 | Figure 2-2: O-DU <sub>8</sub> Hardware Block Diagram                                | 15 |

| 30 | Figure 2-3: Example 2-chip FPGA-based Hardware Acceleration in O-DU <sub>8</sub>    | 19 |

| 31 | Figure 2-4: Example of 1-chip FPGA-based Hardware Acceleration in O-DU <sub>8</sub> | 20 |

| 32 | Figure 2-5: Example of Accelerator Design                                           | 22 |

| 33 | Figure 2-6: Accelerator Design 1 without optional NIC Device                        | 25 |

| 34 | Figure 2-7: Accelerator Design 1 with optional NIC Device                           | 25 |

| 35 | Figure 2-8: Structured ASIC Accelerator Design                                      | 26 |

| 36 | Figure 2-9: Structured ASIC Accelerator Design                                      | 27 |

| 37 | Figure 2-10: O-DU <sub>8</sub> Timing Synchronization                               | 28 |

| 38 | Figure 2-11: HW Acceleration Board Timing and Synchronization                       | 29 |

| 39 | Figure 2-12: External interfaces reference design                                   | 30 |

|    |                                                                                     |    |

#### ORAN.WG7.IPC-HRD-Opt8.0-v03.00

| 1  | Figure 2-13: Mother Board Layout Diagram                                                      |    |

|----|-----------------------------------------------------------------------------------------------|----|

| 2  | Figure 2-14: Chassis Mechanical Diagram                                                       |    |

| 3  | Figure 2-15: High-Level Functional Block Diagram                                              |    |

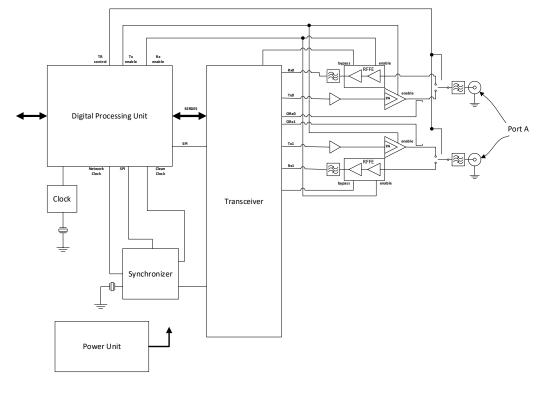

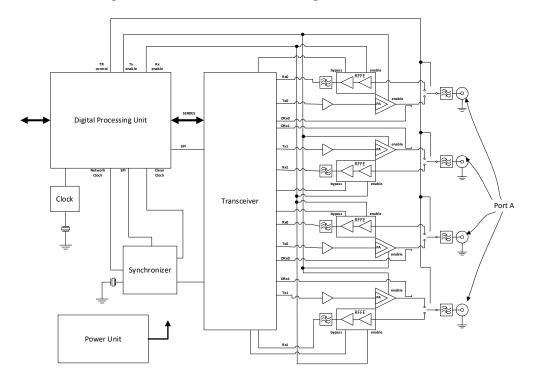

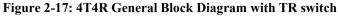

| 4  | Figure 2-16: 2T2R General Block Diagram with TR switch                                        |    |

| 5  | Figure 2-17: 4T4R General Block Diagram with TR switch                                        |    |

| 6  | Figure 2-18: Power estimation for 2T2R O-RU <sub>8</sub>                                      |    |

| 7  | Figure 2-19: Power estimation for 4T4R O-RU <sub>8</sub>                                      |    |

| 8  | Figure 2-20: FPGA Reference Design Diagram                                                    |    |

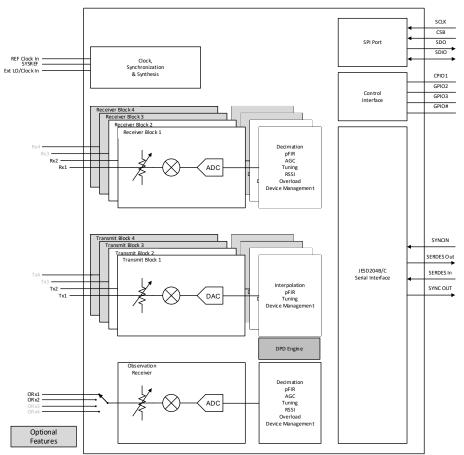

| 9  | Figure 2-21: Transceiver Reference Design Diagram (Optional elements are highlighted in Grey) | 45 |

| 10 | Figure 2-22: PA Reference Design Diagram                                                      | 47 |

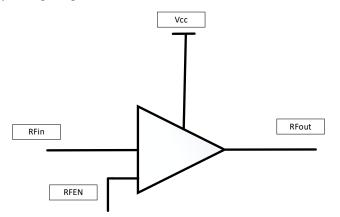

| 11 | Figure 2-23: One Stage LNA Diagram                                                            | 49 |

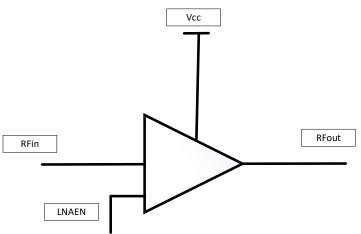

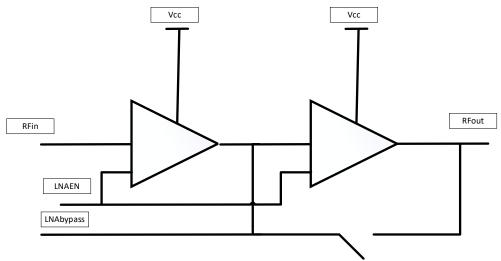

| 12 | Figure 2-24: Two-Stage LNA Diagram                                                            |    |

| 13 | Figure 2-25: RF Switch Reference Design Diagram                                               |    |

| 14 | Figure 2-26: Whip Antenna                                                                     | 53 |

| 15 | Figure 2-27: PLL Reference Design Diagram                                                     |    |

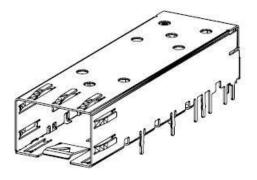

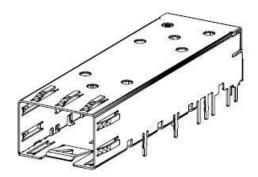

| 16 | Figure 2-28: SFP+ case and connector                                                          |    |

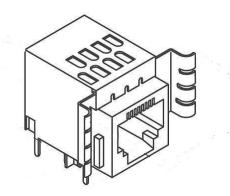

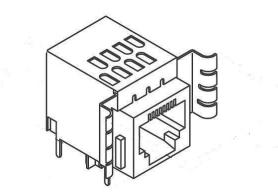

| 17 | Figure 2-29: RJ45 interface                                                                   | 59 |

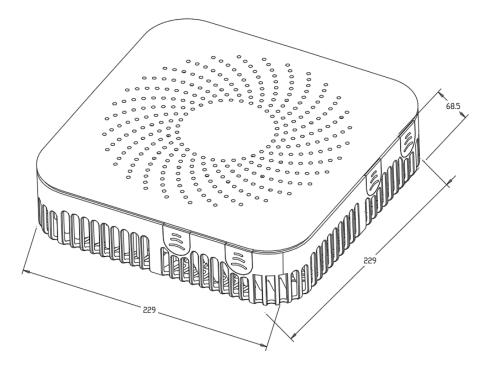

| 18 | Figure 2-30: O-RU <sub>8</sub> Shell Mechanical Diagram                                       | 59 |

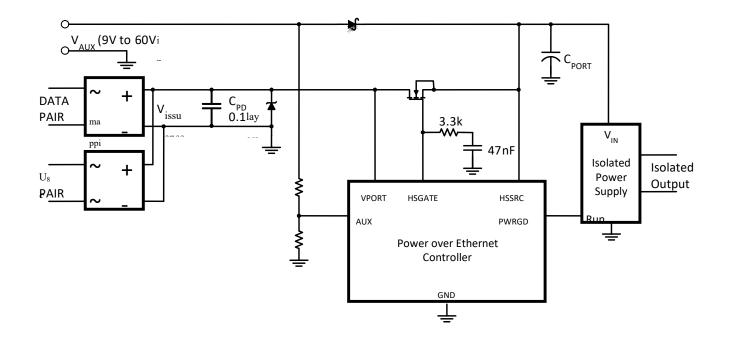

| 19 | Figure 2-31: POE Reference Design Diagram                                                     | 61 |

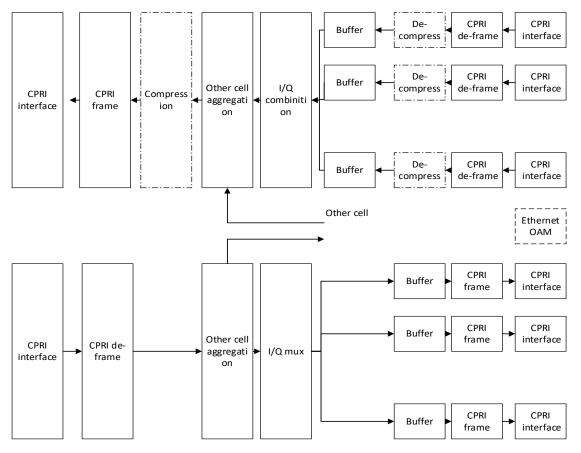

| 20 | Figure 2-32: FHM <sub>8</sub> General Block Diagram                                           |    |

| 21 | Figure 2-33: FHM <sub>8</sub> Digital Processing Block Diagram                                | 64 |

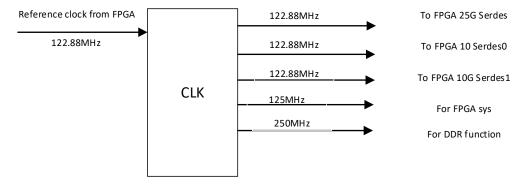

| 22 | Figure 2-34: CLK reference design for FHM8                                                    | 65 |

| 23 | Figure 2-35: SFP+ case and connector                                                          |    |

| 24 | Figure 2-36: RJ45 interface                                                                   | 67 |

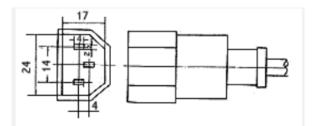

| 25 | Figure 2-37: AC power interface                                                               | 67 |

| 26 | Figure 2-38: Shell Mechanical Diagram                                                         | 68 |

| 27 |                                                                                               |    |

## 1 Chapter 1 Introductory Material

## 2 **1.1 Scope**

3 This Technical Specification has been produced by the O-RAN.org.

The contents of the present document are subject to continuing work within O-RAN WG7 and may change following

formal O-RAN approval. Should the O-RAN.org modify the contents of the present document, it will be re-released by

O-RAN Alliance with an identifying change of release date and an increase in version number as follows:

- Release x.y.z

- 8 where:

7

9

10

11

12

13

14

20

- x the first digit is incremented for all changes of substance, i.e. technical enhancements, corrections, updates, etc. (the initial approved document will have x=01).

- y the second digit is incremented when editorial only changes have been incorporated in the document.

- z the third digit included only in working versions of the document indicating incremental changes during the editing process. This variable is for internal WG7 use only.

- 15 The present document specifies system requirements and high-level architecture for the FR1 Picocell Indoor 16 deployment scenario as specified in the Deployment Scenarios and Base Station Classes document [1].

- In the main body of this specification (in any "chapter") the information contained therein is informative, unless explicitly described as normative. Information contained in an "Annex" to this specification is always informative unless otherwise marked as normative.

## 1.2 References

- The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- [1] ORAN-WG7.DSC.0-V01.00 Technical Specification, 'Deployment Scenarios and Base Station Classes for White

Box Hardware'. <u>https://www.o-ran.org/specifications</u>

- 25 [2] 3GPP TR 21.905: "Vocabulary for 3GPP Specifications".

- [3] 3GPP TR 38.104: "NR; Base Station (BS) radio transmission and reception".

http://www.3gpp.org/ftp//Specs/archive/38\_series/38.104/38104-g10.zip

- [4] ORAN-WG4.CUS.0-v03.00 Technical Specification, 'O-RAN Fronthaul Working Group Control, User and

Synchronization Plane Specification'. <u>https://www.o-ran.org/specifications</u>

- 30 [5] 3GPP TS 38.113:"NR: Base Station (BS) Electromagnetic Compatibility (EMC)".

31 <u>http://www.3gpp.org/ftp//Specs/archive/38\_series/38.113/38113-f80.zip</u>

- [6] ORAN-WG7. IPC. HAR-v01.00 Technical Specification, 'Indoor Pico Cell Hardware Architecture and

Requirement Specification'. <u>https://www.o-ran.org/specifications.</u>

[7] ORAN.WG7. IPC-HRD-Opt7-2.0-v03.00 Technical Specification, 'Indoor Pico Cell BS Hardware Reference

Design Specifications with Fronthaul Split Option 7-2 and FR1'. <u>https://www.o-ran.org/specifications</u>

## 4 1.3 Definitions and Abbreviations

### 5 1.3.1 Definitions

3

For the purposes of the present document, the terms and definitions given in 3GPP TR 21.905 [1] and the following

apply. A term defined in the present document takes precedence over the definition of the same term, if any, in 3GPP

TR 21.905 [2]. For the base station classes of Pico, Micro and Macro, the definitions are given in 3GPP TR 38.104 [3].

9 **Carrier Frequency:** Center frequency of the cell.

10 **F1 interface:** The open interface between O-CU and O-DU<sub>8</sub> as defined by 3GPP TS 38.473 between CU and DU.

11 **Integrated architecture:** In the integrated architecture, the O-RU and O-DU<sub>x</sub> are implemented on one platform. Each 12 O-RU and RF front end is associated with one O-DU<sub>8</sub>. They are then aggregated to O-CU and connected by F1 13 interface.

- 14 **Split architecture:** The  $O-RU_x$  and  $O-DU_x$  are physically separated from one another in this architecture. A switch 15 may aggregate multiple  $O-RU_x$ s to one  $O-DU_x$ .  $O-DU_x$  switch and  $O-RU_x$ s are connected by the fronthaul interface as 16 defined in WG4.

- Transmission Reception Point (TRxP): Antenna array with one or more antenna elements available to the network

located at a specific geographical location for a specific area.

## 19 1.3.2 Abbreviations

For the purposes of the present document, the abbreviations given in [2] and the following apply. An abbreviation defined in the present document takes precedence over the definition of the same abbreviation, if any, as in [2].

| 22 | 7-2   | Fronthaul interface split option as defined by O-RAN WG4, also referred to as 7-2x |

|----|-------|------------------------------------------------------------------------------------|

| 23 | 3GPP  | Third Generation Partnership Project                                               |

| 24 | 5G    | Fifth-Generation Mobile Communications                                             |

| 25 | 5GC   | 5G Core                                                                            |

| 26 | ACS   | Adjacent Channel Selectivity                                                       |

| 27 | ADC   | Analog to Digital Converter                                                        |

| 28 | ASIC  | Application Specific Integrated Circuit                                            |

| 29 | ATA   | Advanced Technology Attachment                                                     |

| 30 | BBDEV | Baseband Device                                                                    |

| 31 | BH    | Backhaul                                                                           |

| 32 | BMC   | Baseboard Management Controller                                                    |

| 33 | BPSK  | Binary Phase Shift Keying                                                          |

| 34 | BS    | Base Station                                                                       |

|    |       |                                                                                    |

Copyright © 2021 O-RAN ALLIANCE e.V.

Your use is subject to the terms of the O-RAN Adopter License Agreement in Annex ZZZ

| 1  | CISPR                    | International Special Committee on Radio Interference                                                                                          |

|----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | CFR                      | Crest Factor Reduction                                                                                                                         |

| 3  | CU                       | Centralized Unit as defined by 3GPP                                                                                                            |

| 4  | COM                      | Cluster Communication                                                                                                                          |

| 5  | CPRI                     | Common Public Radio Interface                                                                                                                  |

| 6  | CPU                      | Central Processing Unit                                                                                                                        |

| 7  | CRC                      | Cyclic Redundancy Check                                                                                                                        |

| 8  | DAC                      | Digital to Analog Converter                                                                                                                    |

| 9  | DDC                      | Digital Down Conversion                                                                                                                        |

| 10 | DDR                      | Double Data Rate                                                                                                                               |

| 11 | DIMM                     | Dual-Inline-Memory-Modules                                                                                                                     |

| 12 | DL                       | Downlink                                                                                                                                       |

| 13 | DPD                      | Digital Pre-Distortion                                                                                                                         |

| 14 | DPDK                     | Data Plane Development Kit                                                                                                                     |

| 15 | DSP                      | Digital Signal Processor                                                                                                                       |

| 16 | DU                       | Distributed Unit as defined by 3GPP                                                                                                            |

| 17 | DUC                      | Digital Up Conversion                                                                                                                          |

| 18 | ECC                      | Error Correcting Code                                                                                                                          |

| 19 | eCPRI                    | evolved Common Public Radio Interface                                                                                                          |

| 20 | EMC                      | Electro Magnetic Compatibility                                                                                                                 |

| 21 | EVM                      | Error Vector Magnitude                                                                                                                         |

| 22 | FCC                      | Federal Communications Commission                                                                                                              |

| 23 | FEC                      | Forward Error Correction                                                                                                                       |

| 24 | FFT                      | Fast Fourier Transform                                                                                                                         |

| 25 | FH                       | Fronthaul                                                                                                                                      |

| 26 | FHGW                     | Fronthaul Gateway                                                                                                                              |

| 27 | FHM <sub>x</sub>         | Fronthaul Multiplexer with no FH protocol translation, supporting an O-DU <sub>x</sub> with split option $x$                                   |

| 28 |                          | and an O-RU <sub>x</sub> with split option x, with currently available options $6 \rightarrow 6$ , 7-2 $\rightarrow$ 7-2 and $8 \rightarrow 8$ |

| 29 | $FHGW_{x \rightarrow y}$ | Fronthaul Gateway that can translate fronthaul protocol from an $O-DU_x$ with split option x to an                                             |

| 30 |                          | O-RU <sub>y</sub> with split option y, with currently available option 7-2 $\rightarrow$ 8.                                                    |

| 31 | FHHL                     | Full Height Half Length                                                                                                                        |

| 32 | FPGA                     | Field Programmable Gate Array                                                                                                                  |

| 33 | GbE                      | Gigabit Ethernet                                                                                                                               |

| 34 | GNSS                     | Global Navigation Satellite System                                                                                                             |

| 35 | GPP                      | General Purpose Processor                                                                                                                      |

| 36 | GPS                      | Global Positioning System                                                                                                                      |

| 37 | HARQ                     | Hybrid Automatic Repeat request                                                                                                                |

| 38 | HHHL                     | Half Height Half Length                                                                                                                        |

| 39 | IEEE                     | Institute of Electrical and Electronics Engineers                                                                                              |

| 40 | IFFT                     | Inverse Fast Fourier Transform                                                                                                                 |

| 41 | IMD                      | Inter Modulation Distortion                                                                                                                    |

|    | Copyright © 2021         | O-RAN ALLIANCE e.V. 10                                                                                                                         |

| 1  | I/O               | Input/Output                                                                                        |

|----|-------------------|-----------------------------------------------------------------------------------------------------|

| 2  | JTAG              | Joint Test Action Group                                                                             |

| 3  | L1                | Layer 1                                                                                             |

| 4  | LDPC              | Low-Density Parity Codes                                                                            |

| 5  | LRDIMM            | Load-Reduced Dual In-line Memory Module                                                             |

| 6  | LTE               | Long Term Evolution                                                                                 |

| 7  | LVDS              | Low-Voltage Differential Signaling                                                                  |

| 8  | MAC               | Media Access Control                                                                                |

| 9  | MCP               | Multi-Chip Package                                                                                  |

| 10 | MH                | Midhaul                                                                                             |

| 11 | MIG               | Memory Interface Generator                                                                          |

| 12 | MII               | Media-Independent interface                                                                         |

| 13 | MIMO              | Multiple Input Multiple Output                                                                      |

| 14 | MU-MIMO           | Multiple User MIMO                                                                                  |

| 15 | NEBS              | Network Equipment-Building System                                                                   |

| 16 | NetConf           | Network Configuration Protocol                                                                      |

| 17 | NFV               | Network Functions Virtualization                                                                    |

| 18 | NIC               | Network Interface Controller                                                                        |

| 19 | NR                | New Radio                                                                                           |

| 20 | O-CU              | O-RAN Centralized Unit as defined by O-RAN                                                          |

| 21 | O-DU <sub>x</sub> | A specific O-RAN Distributed Unit having fronthaul split option x where x may be 6, 7-2 (as         |

| 22 |                   | defined by WG4) or 8                                                                                |

| 23 | O-RU <sub>x</sub> | A specific O-RAN Radio Unit having fronthaul split option x, where x is 6, 7-2 (as defined by       |

| 24 |                   | WG4) or 8, and which is used in a configuration where the fronthaul interface is the same at the O- |

| 25 |                   | DU <sub>x</sub>                                                                                     |

| 26 | OCXO              | Oven Controlled Crystal Oscillator                                                                  |

| 27 | PCIe              | Peripheral Component Interface Express                                                              |

| 28 | PDCP              | Packet Data Convergence Protocol                                                                    |

| 29 | PHY               | Physical Layer                                                                                      |

| 30 | PMBus             | Power Management Bus                                                                                |

| 31 | POE               | Power over Ethernet                                                                                 |

| 32 | PPS               | Pulse Per Second                                                                                    |

| 33 | PRACH             | Physical Random Access Channel                                                                      |

| 34 | QAM               | Quadrature Amplitude Modulation                                                                     |

| 35 | QPSK              | Quadrature Phase Shift Keying                                                                       |

| 36 | QSFP              | Quad Small Form-factor Pluggable                                                                    |

| 37 | RAN               | Radio Access Network                                                                                |

| 38 | RDIMM             | Registered Dual In-line Memory Module                                                               |

| 39 | RF                | Radio Frequency                                                                                     |

| 40 | RoE               | Radio over Ethernet                                                                                 |

| 41 | RU                | Radio Unit as defined by 3GPP                                                                       |

| 1                    | RX                   | Receiver                                                             |

|----------------------|----------------------|----------------------------------------------------------------------|

| 2                    | SATA                 | Serial ATA                                                           |

| 3                    | SDU                  | Service Data Unit                                                    |

| 4                    | SFP                  | Small Form-factor Pluggable                                          |

| 5                    | SFP+                 | Small Form-factor Pluggable plus                                     |

| 6                    | SOC                  | System On Chip                                                       |

| 7                    | SPI                  | Serial Peripheral Interface                                          |

| 8                    | SSD                  | Solid State Drive                                                    |

| 9                    | TCXO                 | Temperature Compensate Crystal Oscillator                            |

|                      |                      |                                                                      |

| 10                   | TDP                  | Thermal Design Power                                                 |

| 10<br>11             | TDP<br>TR            | Thermal Design Power<br>Technical Report                             |

|                      |                      | -                                                                    |

| 11                   | TR                   | Technical Report                                                     |

| 11<br>12             | TR<br>TS             | Technical Report<br>Technical Specification                          |

| 11<br>12<br>13       | TR<br>TS<br>TX       | Technical Report<br>Technical Specification<br>Transmitter           |

| 11<br>12<br>13<br>14 | TR<br>TS<br>TX<br>UL | Technical Report<br>Technical Specification<br>Transmitter<br>Uplink |

2 3

## Chapter 2 Hardware Reference Design 1

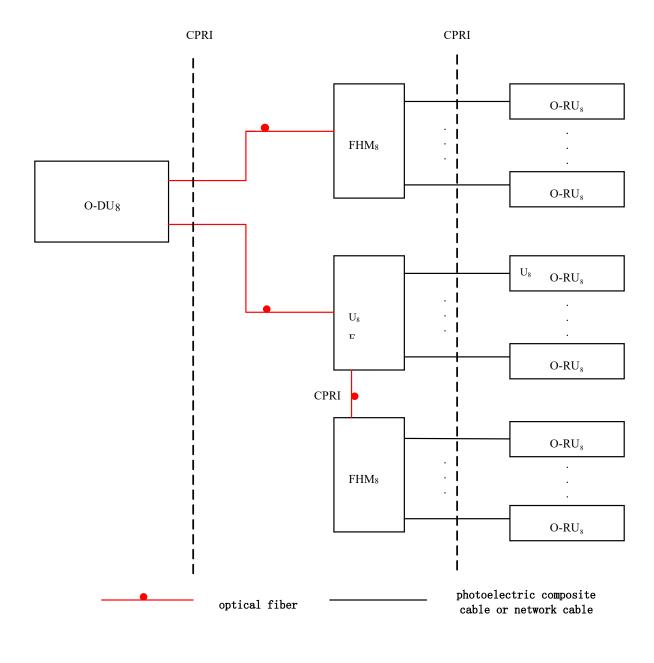

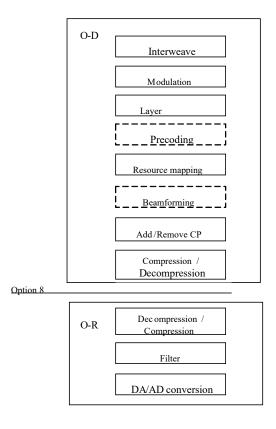

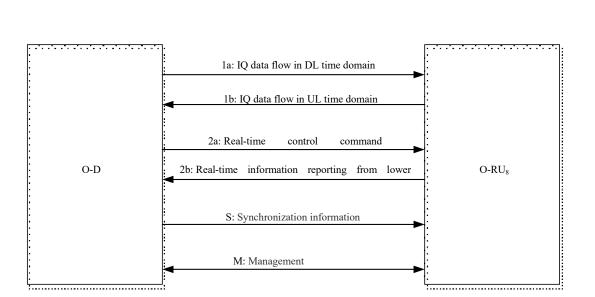

This chapter describes a white box hardware reference design example for indoor Picocell deployment scenario. It includes O-CU, O-DU<sub>8</sub> O-RU<sub>8</sub>, and FHM<sub>8</sub> for IPC deployment scenario.

## 4 2.1 O-CU Hardware Reference Design

The O-CU white box hardware is the platform that perform the O-CU function of upper l2 and l3. The hardware 5 6 systems specified in this document meet the computing, power and environmental requirements of use cases 7 configurations and feature sets of RAN physical node. These requirements are described in the hardware architecture and requirement specification [6] as well as in the use cases document [1]. The O-CU hardware includes the chassis 8 9 platform, mother board, peripheral devices and cooling devices. The mother board contains processing unit, memory, 10 the internal I/O interfaces, and external connection ports. The midhaul (MH) and backhaul (BH) interface are used to carry the traffic between O-CU and O-DU<sub>8</sub> as well as O-CU and core network. The other hardware functional 11 12 components include: the storage for software, hardware and system debugging interfaces, board management controller, just to name a few; the O-CU designer will make decision based on the specific needs of the implementation. 13

14 The HW reference design of O-CU is the same as  $o-du_8$  except for the need of HW accelerator, thus detail design will 15 be described in  $o-du_8$  section 2.2.

## 16 2.2 O-DU<sub>8</sub> Hardware Reference Design

17 The O-DU<sub>8</sub> white box hardware is the platform that performs the DU function of L1 and lower L2. The hardware systems specified in this document meet the computing, power and environmental requirements of use cases 18 19 configurations and feature sets of RAN physical node. These requirements are described in the early hardware 20 requirement specification as well as in the use cases document. The  $O-DU_8$  hardware includes the chassis platform, 21 mother board, peripheral devices and cooling devices. The mother board contains processing unit, memory, the internal 22 I/O interfaces, and external connection ports. The fronthaul and backhaul interface are used to carry the traffic between 23 O-RU<sub>8</sub>/FHM<sub>8</sub> and O-DU<sub>8</sub> as well as O-CU and O-DU<sub>8</sub>. The O-DU<sub>8</sub> design may also provide an interface for hardware 24 accelerator if that option is preferred. The other hardware functional components include: the storage for software, 25 hardware and system debugging interfaces, board management controller, just to name a few; the O-DU<sub>8</sub> designer will 26 make decision based on the specific needs of the implementation.

27 Note that the O-DU<sub>8</sub> HW reference design is also feasible for O-CU and integrated O-CU/ O-DU<sub>8</sub>.

## 28 2.2.1 O-DU<sub>8</sub> High-Level Functional Block Diagram

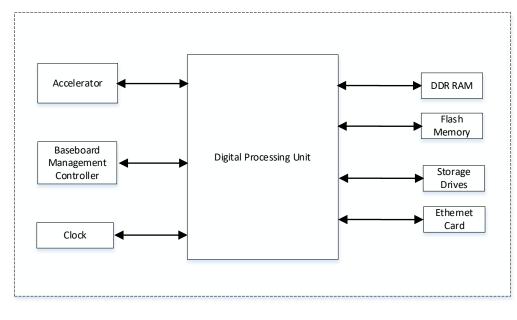

Figure 2-1 shows the major functional blocks of O-DU<sub>8</sub>. The digital processing unit handles the baseband processing workload. To make the processing more efficient, an accelerator can be used to assist with the baseband workload processing. The memory devices include the random-access memory (RAM) for temporary storage of data while flash memory is used for codes and logs. The storage device is for persistent storage. The external network cards can be used

2

3

4

5

for fronthaul or backhaul connection. The baseboard management controller (BMC) is a microcontroller which monitors hardware operation on motherboard. The clock circuits provide digital processing unit with required clock signals.

Figure 2-1: O-DU<sub>8</sub> Functional Block Diagram.

## 6 2.2.2 O-DU<sub>8</sub> Hardware Design Description

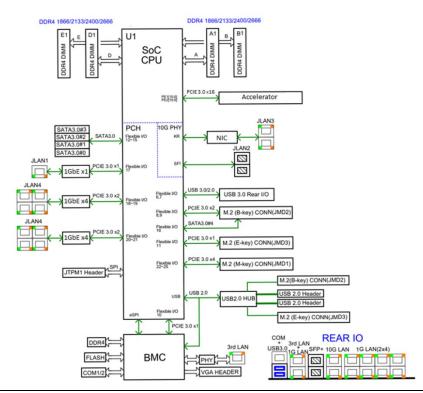

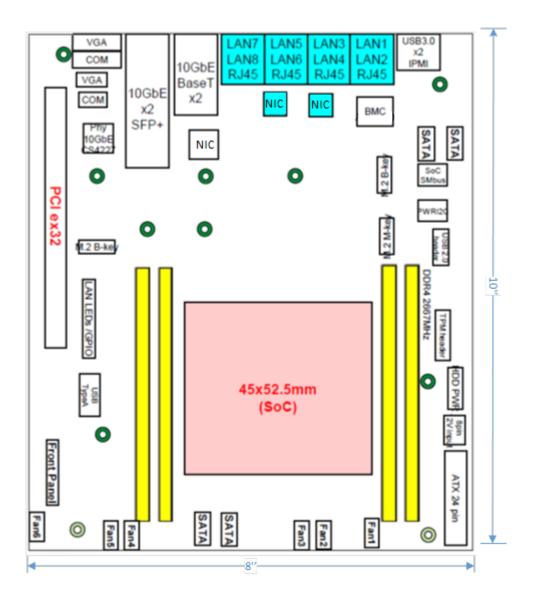

Figure 2-2 describes the components and connections inside the  $O-DU_8$  white box.

#### Figure 2-2: O-DU<sub>8</sub> Hardware Block Diagram

As described in the previous section, the O-DU<sub>8</sub> hardware can be implemented with difference design choices. Here, a system-on-a-chip (SoC) based design is presented as an example which processes most of the O-DU<sub>8</sub> workload. The accelerator can be used to perform some O-DU<sub>8</sub> workload functions based on the overall performance requirement. Several Ethernet controllers are used for front haul link, back haul link and remote console control connection. The other parts include: RAM, flash memory, and hard drive storage. The JTAG and USB ports are provided for hardware debug and local connection if needed. Figure 2-2 describes the components and connections of O-DU<sub>8</sub> hardware. Finally, BMC block is mainly responsible for monitoring the hardware status.

## 9 2.2.3 O-DU<sub>8</sub> Hardware Components

In this section, the details of the  $O-DU_8$  hardware component's requirements, features and parameters are described. The components selection is based on the use case requirements which are listed in the hardware architecture and requirements document [6].

#### 13 2.2.3.1 Digital Processing Unit

14 This example of the digital processing unit in  $O-DU_8$  is based on the General Purpose Processor (GPP).

#### a. Digital Processing Unit Requirement

- 16 The GPP requirements are listed in the following table.

- 17

15

1

| Table 2-1: The | Processor | Feature List |

|----------------|-----------|--------------|

|----------------|-----------|--------------|

| Item Name                                  | Description |

|--------------------------------------------|-------------|

| # of Cores                                 | 16          |

| # of Threads                               | 32          |

| Base Frequency                             | 2.20 GHz    |

| Max Turbo Frequency                        | 3.00 GHz    |

| Cache                                      | 22 MB       |

| Thermal Design Power (TDP)                 | 100W        |

| Max Memory Size (dependent on memory type) | 512 GB      |

| Memory Types                               | DDR4        |

| Max # of Memory Channels                   | 4           |

18 19

20

- The interface specifications on the main board are as follows:

- **Memory Channel Interfaces:** The system memory capacity, type and related information are described in the following table.

- 21 22

23

| Tabla 2_2. Tha   | Momory Cl | hannel Feature L | ict |

|------------------|-----------|------------------|-----|

| 1 auto 2-2. 1 no |           | iannei reature L | 151 |

| Item Name            | Description       |

|----------------------|-------------------|

| Memory Types         | DDR4              |

| # of Memory Channels | 4                 |

| ECC LRDIMM           | Up to 512GB       |

| ECC RDIMM            | Up to 256GB       |

| Memory Speed         | 2666/2400/2133MHz |

Copyright © 2021 O-RAN ALLIANCE e.V.

2

3

4

5 6

7

8

9

10

11

12

13

26

33

34

35

37

38

| DIMM Sizes     | 128GB, 64GB, 32GB, 16GB |

|----------------|-------------------------|

| Memory Voltage | 1.2 V                   |

**PCIe:** PCIe Gen 3 should be supported by the processor. There are total of 32 PCIe lanes with 128 Gb/s bandwidth. The 32 PCIe lanes can be divided into two x16 slots by using a riser card.

**Ethernet:** The system should be capable to offer aggregated 48 Gb/s Ethernet bandwidth. The breakout the ports are discussed in later section. When higher Ethernet bandwidth required, an Ethernet card can be installed in one of the PCIe slot.

#### b. Digital Processing Unit Design

The digital processing unit is a SoC device which is a 64-bit multi-core server class processor. This SoC includes an integrated Platform Controller Hub (PCH), integrated high-speed I/O, Integrated Memory Controllers (IMC), and four integrated 10 Gigabit Ethernet ports.

The SOC supports 512-bit wide vector processing instruction set. It also supports hardware virtualization to enable dynamic provisioning of services as communication service providers extend network functions virtualization (NFV). Figure 2-2 shows the major functional blocks of the digital processing unit.

#### 14 2.2.3.2 Hardware Accelerator

Hardware accelerators can be used in  $O-DU_8$  to offload computationally intensive functions and to optimize the performance under varying traffic and loading conditions. The acceleration functional requirements and implementation are system designer's choice; however, the  $O-DU_8$  shall meet the minimum system performance requirements under various loading and deployment conditions. In most cases, a Field Programmable Gate Array (FPGA) or Application Specific Integrated Circuit (ASIC) based PCIe card can be used to optimize the system performance. The FPGA(s) are part of a Network Interface Controller (NIC) that further provides connectivity services.

#### 21 2.2.3.2.1 Accelerator Design Solution 1

The O-DU<sub>8</sub> system is typically implemented using a multi-core processor and one or more hardware accelerators. Parts of O-DU<sub>8</sub> protocol stack can be implemented in software running on the multi-core processors, some of the computationally intensive L1 and L2 functions are offloaded to FPGA-based or similar hardware accelerators. This is a programmable hardware, which provides both flexibility and high computing capabilities.

a. Accelerator Requirements

The accelerator unit comprises one or more FPGAs (e.g., two FPGAs), sufficient amount of DDR4 memory, and synchronization circuitry where one of FPGAs is used for L1 functional offload and the other one is used to perform fronthaul connectivity functions/protocols. The FPGA for L1 offload uses dedicated cores for channel encoding/decoding as well as FPGA and processing resources for running L1 functions such as but not limited to rate matching and de-matching, interleaving and scrambling, demodulation and HARQ buffer management as well as OFDM modulation/demodulation and channel estimation.

- Key features of the FPGA-based accelerator include:

- 2X10/25G CPRI or RoE fronthaul interface

- Built-in SyncE/IEEE1588v2 synchronization + external reference timing

- 36 L1 offloading options

- LDPC encoding and decoding

- Polar encoding and decoding

- HARQ management with on board DDR memory (including DDR controller and interfaces)

- Other L1 offloading candidates include PRACH detection, MIMO encoding and decoding, channel estimation

- Partial or full L1 functions can be offloaded. It is recommended to offload the user-plane channel coding chain and part of or the entire control-plane channel coding chain to the hardware accelerator.

- PCIe Gen3 x16, two Gen4 x8, or PCIe Gen3 x16 bifurcated to two Gen3 x8

- GPP supported

- Standard PCIe FHHL card (It is assumed that the hardware accelerators further perform NIC functions).

- 8GB DDR4 memory for buffering

- Power consumption not to exceed 75W

- The accelerator requirements in hardware have been summarized inTable 2-3.

- 13

2 3

4

5

6

7

8

9

10

11

12

#### Table 2-3: Accelerator Hardware Component List

| Item Name                      | Description for FPGA 1                                                                                  | Description for FPGA 2                        |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

|                                | System Logic cells - 930K                                                                               | System Logic cells - 1,143K                   |  |

|                                | CLB LUT - 425K                                                                                          | CLB LUT - 523K                                |  |

| SoC Resources                  | SDFEC -8                                                                                                | CLB Flip-Flops -1,045K                        |  |

| Soc Resources                  | DSP Slices - 4,272                                                                                      | DSP Slices - 1,968                            |  |

|                                | BRAM - 38.0Mb                                                                                           | BRAM - 34.6Mb                                 |  |

|                                | URAM - 22.5Mb                                                                                           | URAM - 36.0Mb                                 |  |

| Form Factor                    | FHHL PCIe Form Factor                                                                                   |                                               |  |

|                                | x8 Gen1, Gen2, Gen3 interface to FPGA2 and                                                              |                                               |  |

| PCIe Interface                 | <ul><li>x8 Gen1, Gen2, Gen3 interface to FPGA1</li><li>have x16 to two x8 bifurcation</li></ul>         |                                               |  |

|                                |                                                                                                         |                                               |  |

|                                | FPGA1                                                                                                   | FPGA2                                         |  |

| On Board<br>Memory             | Total Capacity 4 GB in PL, upgradeable to 8GB                                                           | Total Capacity 4 GB in PL, upgradeable to 8GB |  |

| ,                              | Total Capacity 2 GB in PS, upgradeable to 4GB                                                           | Total Capacity 2 GB in PS, upgradeable to 4GB |  |

| Network                        | N//                                                                                                     | 2xSFP28 optical interfaces to FPGA2           |  |

| Interface(s)                   | N/A                                                                                                     | (User Configurable, includes 10/25 Ethernet)  |  |

| Other External<br>Interface(s) | Micro USB for JTAG support (FPGA programming and debug) and access to BMC                               |                                               |  |

| Graphical<br>User interface    | GUI for monitoring the basic board parameters, monitoring temperature alerts, firmware upgrades for BMC |                                               |  |

|                          | Power sequencing and reset                                    |

|--------------------------|---------------------------------------------------------------|

|                          | • Field upgrades                                              |

| Board                    | • FPGA configuration and control                              |

| Management<br>Controller | Clock configuration                                           |

|                          | • I2C bus access                                              |

|                          | • USB 2.0                                                     |

| Operating<br>Temperature | -5°C - 55°C                                                   |

| Power                    | < 75 W                                                        |

| Clocking                 | Low-Jitter, configurable clock ranging from10MHz to 750MHz    |

| Options                  | 1 PPS input and output with assembly option for OCXO and TCXO |

The following are the accelerator requirements in function and interface.

#### **Functional offload requirements**

One of the candidate functions for offloading is the LDPC encoder and decoder, which typically consists of computationally intensive and relatively highly power-consuming functions. It must be noted that neither software implementation in CPU nor soft FPGA logic implementation would provide a highly power-efficient solution while meeting/exceeding 3GPP NR user-plane encoder/decoder throughput and latency requirements, rather a hardened implementation of the FEC functions would be very power efficient. Downlink and uplink throughputs of up to 40Gbps and 18Gbps, respectively, are shown feasible with this architecture. Other candidate L1 functions for acceleration include CRC generation, segmentation, bit-level/sub-block interleaving and scrambling as well as FFT/IFFT processing, for which an FPGA can be used.

For other symbol processing L1 functions, which require heavy multiply and accumulation operations, FPGAs 1 and 2 have DSP blocks that can efficiently perform these operations. Polar encoding and/or decoding on the control-plane can also be offloaded to FPGA1 resulting in high throughputs and low latencies.

#### **Interface requirements**

- PCIe: PCIe interface is widely used to provide interface between the GPP and hardware accelerators. FPGA devices have dedicated PCIe hard IP which facilitate implementation and quick setup of PCIe interface. They support both PCIe Gen3 x16 or PCIe Gen4 x8, which allow the FPGA device to interface with any GPP supporting either PCIe Gen3 x16 or PCIe Gen4 x8 interface.

# Fronthaul: FPGA devices can support various speed grades and any fronthaul protocols, customers can use off-the-shelf CPRI or RoE IPs to quickly implement and configure any fronthaul interface protocol.

- Serial transceivers: FPGA devices have SerDes resources to implement various connectivity speeds (e.g.,

33 Gb/s) per SerDes, 10G/25G CPRI, 10G/25G/50G/100G Ethernet connections can use these SerDes

resources.

- Ethernet MAC speed: FPGA devices have hardened implementations of Ethernet MAC that support speeds

of 100 Gb/s and above. The Ethernet MAC IP allows power-efficient implementation of high speed Ethernet

connectivity. In the example shown in Figure 2-3, FPGA 1 and FPGA 2 can use the hard 100Gbps MAC IPs to

connect each other, allowing the L1 and fronthaul functions to be distributed across these two FPGAs with less

connectivity overhead. For other Ethernet MACs such as 10G/25G Ethernet, they provide soft Ethernet MAC IPs, so when implementing CPRI or RoE fronthaul functions, 10G/25G Ethernet MAC can be used.

b. Accelerator Design

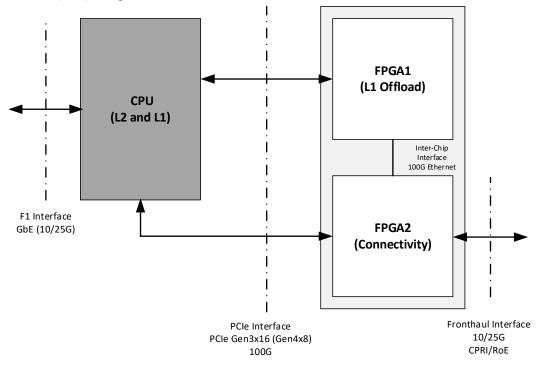

The hardware accelerator supports GPP. Figure 2-3 illustrates a two-chip acceleration architecture comprising two FPGAs with multi-lane PCIe interfaces toward the CPU and external connectivity toward O-RU<sub>8</sub>(s) via CPRI/RoE and O-CU(s) through GbE connectivity. The example architecture further depicts multi-lane Gen3 or Gen4 PCIe interfaces between each FPGA and the CPU. The FPGAs communicate through high-bandwidth Ethernet (GbE) transport.

Figure 2-3: Example 2-chip FPGA-based Hardware Acceleration in O-DU8

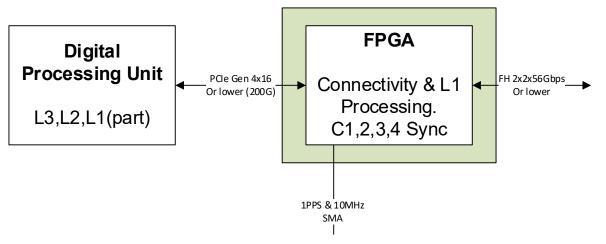

#### 1 2.2.3.2.2 Accelerator Design Solution 2

example, or Gen4) between FPGA and the CPU.

2 This section illustrates a one-chip acceleration architecture comprising one FPGA with PCIe interfaces toward the CPU

and external connectivity toward O-RU8(s). The example architecture further depicts Gen3 PCIe interfaces (for

3 4

5

An example one-chip FPGA-based hardware acceleration architecture is shown in Figure 2-4.

## 6 7

8

9

10

11

12

13

14

15

16

17

18

20

21

#### Figure 2-4: Example of 1-chip FPGA-based Hardware Acceleration in O-DU8

#### a. Accelerator Requirement

The accelerator unit comprises one or more FPGAs (e.g., two FPGAs), sufficient amount of DDR4 memory, and synchronization circuitry where one of FPGAs is used for L1 functional offload and the other one is used to perform fronthaul connectivity functions/protocols. The FPGA for L1 offload uses dedicated cores for channel encoding/decoding as well as FPGA and processing resources for running L1 functions such as but not limited to rate matching and de-matching, interleaving and scrambling, demodulation and HARQ buffer management as well as OFDM modulation/demodulation and channel estimation.

- Key features of the FPGA-based accelerator include:

- 4X25G/10G CPRI optical interface

- 1x10G Ethernet optical interface

- Support GNSS/IEEE1588v2+syncE reference timing

- 19 L1 offloading options

- LDPC encoding and decoding

- HARQ management

2

3

4 5

6

7

8 9

10 11

12

13

15

16 17

18 19

20

- Other optional L1 offloading such as FFT/IFFT, CP, CRC, rate matching, PRACH detection.

- PCIe Gen3X16, 4 hard IP blocks

- FHHL form factor and operation temperature from -5°C to +55°C

- 2GB DDR4 memory for Buffering

- Specific power supply design is required with 1-chip FPGA, since the maximum power consumption of PCIe specification (75w) could be exceeded, additional external auxiliary power may be required.

#### **Functional offload requirements**

- L1 offloading: One of the functions for L1 offloading is the LDPC encoder and decoder, which typically consists of computationally-intensive and relatively highly power-consuming functions. Other L1 functions for acceleration include CRC generation, CP, PRACH detection and rate matching as well as FFT/IFFT processing.

- **Fronthaul:** The data transmission and protocol processing of fronthaul interface is completed on the FPGA device.

#### 14 Interface requirements

- PCIe: PCIe interface is widely used to provide interface between the CPU and hardware accelerators. FPGA device has dedicated PCIe hard IP which facilitate implementation and quick setup of PCIe interface. FPGA support PCIe Gen3 x16, which allow the FPGA device to interface with any CPU supporting either PCIe Gen3 x16 interface.

- Fronthaul: FPGA device can support various speed grades and CPRI protocol for fronthaul interface between O-DU<sub>8</sub> and O-RU<sub>8</sub>.

- Backhaul: FPGA device can support backhaul interface between O-DU<sub>8</sub> and core network function with an

10G optical interface.

- Synchronization: Accelerator has external interfaces to support synchronization, including GNSS,

IEEE1588v2 and SyncE reference timing.

Copyright © 2021 O-RAN ALLIANCE e.V.

2

3

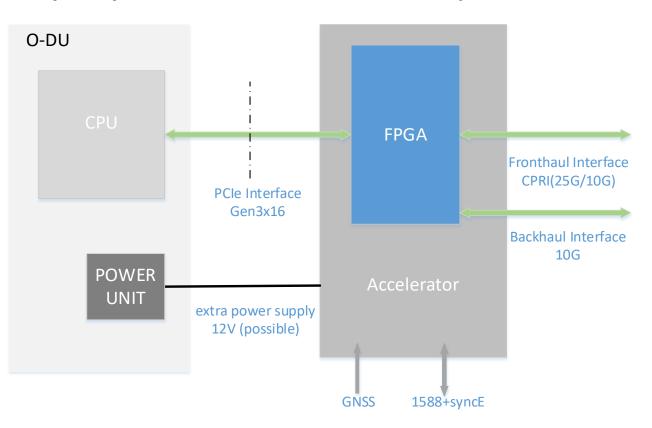

#### b. Accelerator Design

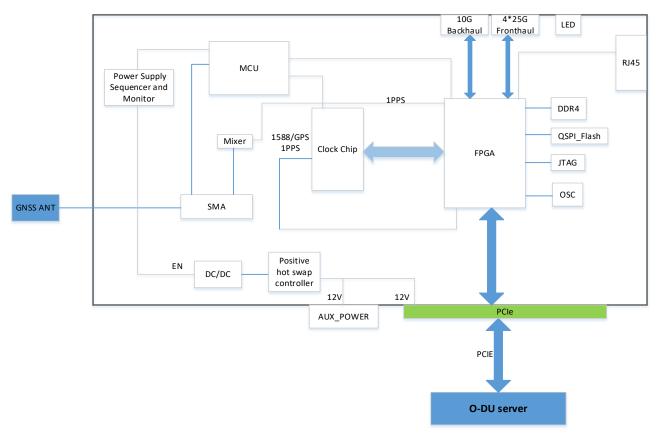

Figure 2-5: Example of Accelerator Design

2

3

4

5

6

25

27

28

29

Figure 2-5 shows the accelerator design, description of block diagram of board card:

**12V power:** The maximum power consumption of the whole card is estimated to exceed 75W. The PCIe cannot meet the power consumption demand, so it needs an external 12V auxiliary power supply. The extra power consumption can be included by the power unit of O-DU<sub>8</sub>. Only power cord is needed, and it has no effect on the whole machine design. This part is not necessary if there are future optimizations.

- **DC/DC:** The module contains all the power sources used in the system.

- Power Supply Sequencer and Monitor: Since the system has the power on timing requirement, this module

controls the output of each DC/DC to realize the normal power on/off of the system.

- 9 Mixer and GNSS antenna: The system uses an external antenna, which can be placed outdoors to improve 10 the receiving sensitivity of synchronizing signal. After mixer's processing of the received signal, the signal 11 source of 1pps is output to clock chip for system input synchronous clock signal.

- MCU (micro control unit): As the auxiliary processor of the board card, MCU realizes the temperature detection of the board card, the operation state indication and the configuration of power monitor and clock chip in the initialization process, and real-time monitoring of the working state of each module, exception handling and other functions.

- Clock chip: The chip realizes system-level clock input, which can synchronously output all kinds of clocks for

clock synchronization of subordinate modules.

- FPGA: As the core chip of the board card, FPGA forwards the data of the downlink of the core network and

the uplink data gathered at the O-RU<sub>8</sub>(s), and interacts with the O-DU<sub>8</sub> server through PCIe x16 to complete

the calculation of 5G NR data.

- 21 2.2.3.2.3 Accelerator Design Solution 3

- Channel coding for LDPC and fronthaul compression requires a significant amount of bit level processing and is well

suited to a fine-grained FPGA architecture and/or low cost/power structured ASIC. Options include:

- Look-aside FEC: LDPC (de)coding, Polar (de)coding, Rate (De)Matcher, (De) Interleaver, CRC, HARQ

- L1 Processing: (i)FFT & CP+/-, PRACH, channel estimation & beamforming

- Bump-in-wire Fronthaul: compression / decompression for latency and bandwidth reduction

- a. Accelerator Requirement

- Hardware requirements are listed in Table 2-4.

#### **Table 2-4: Accelerator Hardware Feature List**

| Item Name                                     | Description           |

|-----------------------------------------------|-----------------------|

| PCIe (Interface with digital processing unit) | Gen4 x16 (and lower)  |

| Form factor                                   | FHHL                  |

| Connectivity                                  | 2x QSFP28/56          |

| FPGA                                          | Logic Elements: 1437K |

|                                               | M20K Memory: 139Mb    |

Copyright © 2021 O-RAN ALLIANCE e.V.

|                                 | Quad-core GPP Hard Processor Sub-system                                                            |  |

|---------------------------------|----------------------------------------------------------------------------------------------------|--|

| NIC Device                      | 100Gb xHAUL for FH, BH & MH traffic shaping. Optional FPGA co-processing.                          |  |

| DDR Main                        | 8+8+1GB DDR4                                                                                       |  |

| Flash (FPGA images)             | >=1 Gbit                                                                                           |  |

| BMC                             | Telemetry, Security, remote upgrade                                                                |  |

| Clocking                        | For O-RAN C1, C2, C3 & C4                                                                          |  |

| Fronthaul                       | CPRI                                                                                               |  |

| GPS                             | SMA for 1PPS & 10MHz (in/out)                                                                      |  |

| Operating Temperature (ambient) | NEBS Compliant                                                                                     |  |

| Power                           | <75W (without optional NIC device)                                                                 |  |

| Clock Accuracy                  | Low-Jitter, configurable clock ranging from 10MHz to 750MHz.<br>Option for OCXO (TCXO as standard) |  |

Firmware Requirements are listed in Table 2-5.

#### Table 2-5: Accelerator Firmware Feature List

| Item Name                           | Description                                                                                                                   |  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| Remote system upgrade               | Securely upgradable FPGA flash image                                                                                          |  |  |

| Queuing                             | 64 Queues supported equally split between UL & DL.                                                                            |  |  |

|                                     | NR LDPC Encoding with, interleaving and rate-matching.                                                                        |  |  |

| LDPC Acceleration                   | NR LDPC Decoding with sub-block de-interleaving function of reverse rate matching.                                            |  |  |

|                                     | Early Termination, CRC attachment and HARQ buffering.                                                                         |  |  |

|                                     | 5G Throughput: DL 14.8Gbps, UL 3.2Gbps                                                                                        |  |  |

| Load Balancing (channel coding)     | Load balancer distributes the pending encoder/decoder requests to encoder/decoders                                            |  |  |

|                                     | Code block based interface.                                                                                                   |  |  |

| Descriptor Formet (shormed as dire) | Software enablement by BBDEV API (DPDK)                                                                                       |  |  |

| Descriptor Format (channel coding)  | https://www.dpdk.org/                                                                                                         |  |  |

|                                     | https://doc.dpdk.org/guides/prog_guide/bbdev.html                                                                             |  |  |

| Fronthaul Compression               | In-line compression/decompression for Mu-Law, block-floating point and quantization according to the O-RAN WG4 specification. |  |  |

| Open programmable acceleration      | Support for:                                                                                                                  |  |  |

| environment | • | FPGA Flashing upgrade                         |

|-------------|---|-----------------------------------------------|

|             | • | Firmware version reporting                    |

|             | • | PCIe diagnostics                              |

|             | • | Ethernet diagnostics                          |

|             | • | Temperature and voltage telemetry information |

3

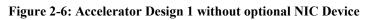

#### b. Accelerator Design

Accelerator design solution 3 has 2 options as shown in the figures below.

6

7

4

5

The accelerator with optional NIC device.

Figure 2-7: Accelerator Design 1 with optional NIC Device

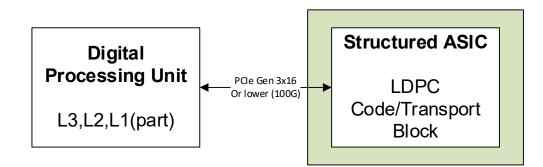

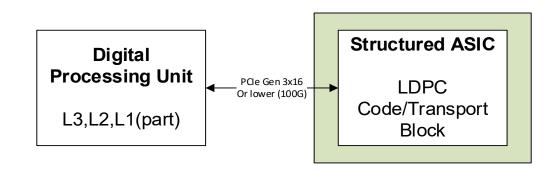

#### Figure 2-8: Structured ASIC Accelerator Design

#### 2.2.3.2.4 Accelerator Design Solution 4

Channel coding for LDPC and fronthaul compression requires a significant amount of bit level processing and is well suited to a fine-grained structured ASIC. Features include:

- Look-aside FEC: Turbo (de)coding, LDPC (de)coding, Rate (De)Matcher, (De) Interleaver, CRC, HARQ retransmission & (de)interleaver.

- a. Accelerator Requirement

- Hardware features are listed in Table 2-6.

- 11

1

2

3

4

5

6

7

8

9

10

#### Table 2-6: Accelerator Hardware Feature List

| Item Name                   | Description                                               |

|-----------------------------|-----------------------------------------------------------|

| PCIe                        | Gen3 x16                                                  |

| Form factor                 | HHHL                                                      |

| DDR                         | DDR4 (64-bit +ECC), 2667Mbps Interface for HARQ buffering |

| Board Management Controller | Telemetry, Security.                                      |

| Power                       | <35W                                                      |

12

13

Firmware Requirements are listed in Table 2-7.

#### 14

#### Table 2-7: Accelerator Firmware Feature List

| Item Name         | Description                                                                        |

|-------------------|------------------------------------------------------------------------------------|

| Queuing           | 64 Queues supported equally split between UL & DL.                                 |

|                   | NR LDPC Encoding with, interleaving and rate-matching.                             |

| LDPC Acceleration | NR LDPC Decoding with sub-block de-interleaving function of reverse rate matching. |

|                                                                                                                 | Early Termination, CRC attachment and HARQ buffering. |  |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

|                                                                                                                 | 5G Throughput: DL 23Gbps, UL 8Gbps                    |  |

| Load Balancing (channel coding)       Load balancer distributes the pending encoder/decoder in encoder/decoders |                                                       |  |

| Descriptor Format (channel coding)                                                                              | Code block and transport block based interface.       |  |

|                                                                                                                 | Software enablement by BBDEV API (DPDK)               |  |

|                                                                                                                 | https://www.dpdk.org/                                 |  |

|                                                                                                                 | https://doc.dpdk.org/guides/prog_guide/bbdev.html     |  |

3

4

b. Accelerator Design

The following diagram shows the structured ASIC based accelerator design.

Figure 2-9: Structured ASIC Accelerator Design

7

5

6

### 8 2.2.3.3 Baseboard Management Controller

9 BMC is used to perform hardware power control (power on, power off and power cycle), monitor hardware status 10 (temperatures, voltages, etc.), monitor Basic I/O System (BIOS)/ Unified Extensible Firmware Interface (UEFI) 11 firmware status, and log system events. It provides remote access via shared or dedicated NIC. System user can do 12 console access via serial or physical/Kernel-based Virtual Machine (KVM). The BMC has dedicated RAM and flash 13 memory. It provides access via serial port or Ethernet port. Figure 2-2 describes the BMC connections with related 14 components.

15

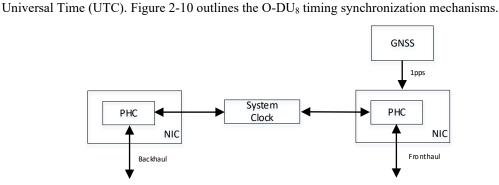

## 16 2.2.4 Synchronization and Timing

### 17 2.2.4.1 Synchronization and Timing Design 1

18 This section describes the synchronization and timing mechanism that is used in the  $O-DU_8$ . Copyright © 2021 O-RAN ALLIANCE e.V.

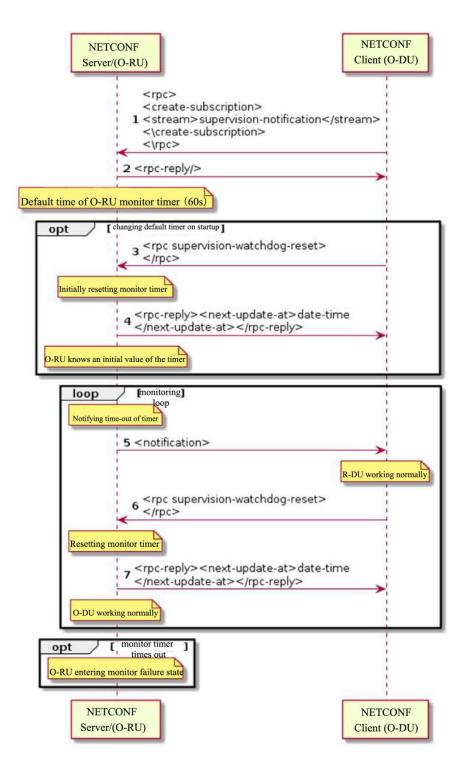

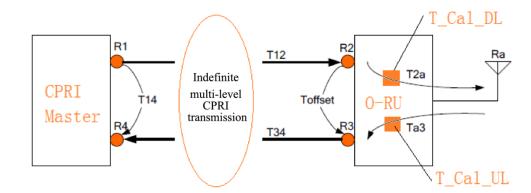

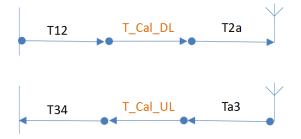

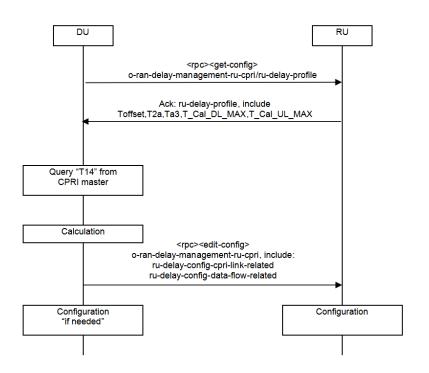

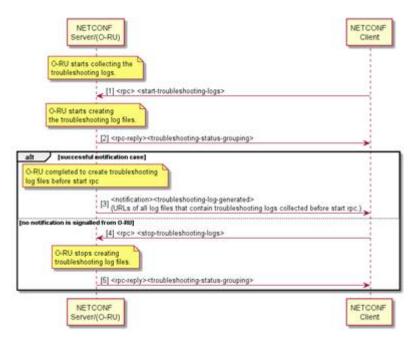

Hardware Requirements 1 a. The O-DU<sub>8</sub> shall support following timing synchronization methods: 2 3 1. **GPS** Synchronization Ethernet based IEEE1588v2 Synchronization 4 2. BeiDou Synchronization 5 3. BeiDou and GPS switching 6 4. b. Hardware Design 7 8 Depending on the timing distribution topologies used, the O-DU<sub>8</sub> system clock is able to synchronize with the 9 Grand Master Clock (GMC) using IEEE1588 via either the front haul NIC or backhaul NIC. O-DU<sub>8</sub> can also 10 synchronize timing using Global Navigation Satellite System (GNSS). In the case of IEEE1588, the Physical Hardware Clock (PHC) within the NIC is synchronized with the GMC first, then the O-DU<sub>8</sub> system clock is 11 12 synchronized with the PHC. The O-DU<sub>8</sub> is also capable to provide clock to the O-RU<sub>8</sub> via front haul if needed. When GNSS becomes available to O-DU<sub>8</sub>, it will be able to synchronize the system clock to Coordinated 13 14

15

16

Figure 2-10: O-DU<sub>8</sub> Timing Synchronization

17

20

21

22 23

24

25

26 27

28

29

30

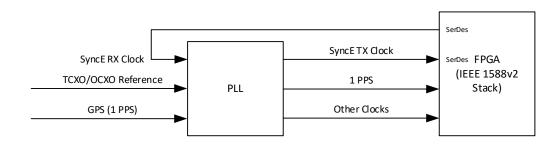

#### 18 2.2.4.2 Synchronization and Timing Design 2

- 19 This section describes the synchronization and timing mechanism that is used in the hardware accelerator board.

- a. Hardware Requirements

- Each hardware accelerator board that supports connectivity functions in  $O-DU_8$  must be able to support external synchronization I/O and to receive or transmit 1 PPS reference clock source in order to ensure synchronization across network.

- b. Hardware Design

- The accelerator board can operate in the master or slave mode when supporting IEEE 1588v2 timing/synchronization. It can generate 1 PPS reference clock for synchronization in the master mode and can receive the 1 PPS reference clock in the slave mode for internal synchronization. The timing circuitry of the accelerator board is shown in Figure 2-11. Two FPGA SerDes transceivers are used to receive and transmit SyncE TX and RX clocks.

#### Figure 2-11: HW Acceleration Board Timing and Synchronization

## 4 2.2.5 External Interface Ports

5 The external interfaces of  $O-DU_8$  are described below.

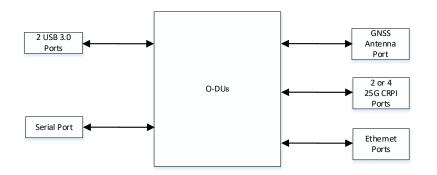

#### a. Hardware Requirements

The following table shows the external ports or slots that the system provided.

7 8

6

1

2

3

| Table  | 2-8: | External  | Port List   |

|--------|------|-----------|-------------|

| I HOIC | - 0. | DATE: Hut | I OI C LISC |

| Item Name    | Description                               |

|--------------|-------------------------------------------|

| Ethernet     | Octave Gigabit Ethernet LAN connectors    |

|              | Dual 10GbE Base-T Ethernet connectors     |

|              | Dual 10GbE SFP+ Faber Ethernet connectors |

|              | 2x100G QSFP28 or 2x25G SFP28              |

| USB          | 2 USB 3.0 ports                           |

| Serial Port  | 1 COM port via RJ45                       |

| Antenna port | 1 SMA connector for GNSS                  |

#### 9

10

11

12

13

14

15 16

#### **b.** Hardware Design

The digital processing unit is a SoC device which provides the external ports described in the hardware requirement section. The system includes 2 USB 3.0 ports, and the serial RS232 port that can be used for Console Redirection, e.g. Out-of-Band Management. The system provides eight 1Gbps and four 10Gbps Ethernet ports. There are two or four 25G CPRI ports in system depends on the accelerator card used. The system also provides a RF interface to connect GNSS antenna. The following diagram outlines the external interfaces that supported.

2

#### Figure 2-12: External interfaces reference design

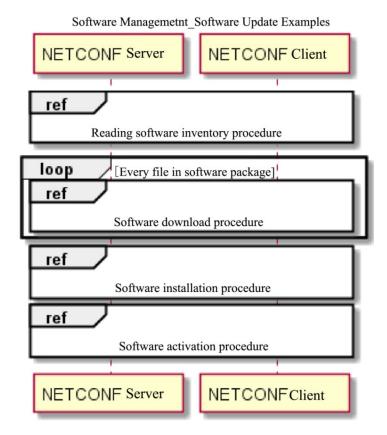

## 3 2.2.6 O-DU<sub>8</sub> Firmware

- 4 BIOS and BMC firmware are needed in the system and shall be installed.

- 5

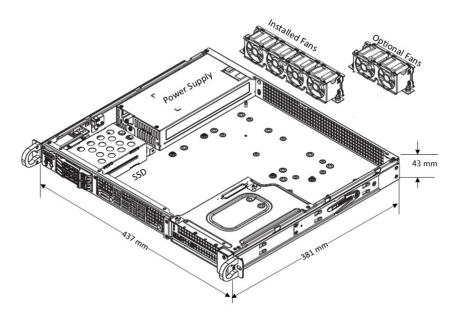

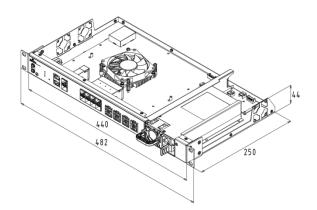

## 1 2.2.7 Mechanical

3

4

5

6

7